インテル、「3次元」で逆襲

積層CPU、待機電力9割減 微細化競争で限界見据え

Nikkei Online, 2020年12月8日 2:00

レノボの画面を折り畳めるパソコンに

インテルの3次元技術を使った半導体が搭載

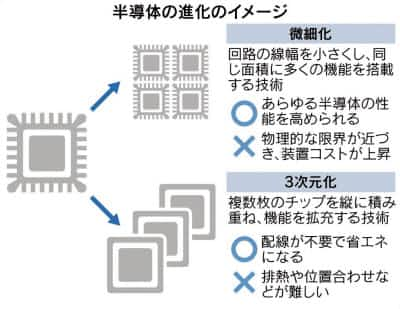

半導体の開発競争でチップを積み重ねる「3次元」の重みが増してきた。米インテルは6月にパソコン用CPU(中央演算処理装置)で新製品を投入し、省エネ性能を高めた。台湾積体電路製造(TSMC)は米グーグルと協業を進める。3次元関連の市場規模は2024年に1.2兆円を超え、装置や部材メーカーを巻き込んだ競争が激化する。

中国レノボ・グループが10月、画面を折りたためるパソコンを世界で初めて発売した。開くと13.3型の大型タブレットとして使える。画面を曲げるとキーボードが表示され、小型のノートパソコンに変身する。

この端末の頭脳を担うのが、インテルが6月に発売したCPUだ。

インテルはこれまで、「電源」「計算」「記憶」のそれぞれを担う機能を平面に並べていた。新製品では3階建ての家のように、チップを立体的に積み重ねた。配線による電力ロスがなくなるため、待機電力を9割減らせる。階層を1つ積み上げるごとにデータ処理のエネルギー効率が3倍になるという。

「進化の試金石」

スマートフォンなどに使われるフラッシュメモリーでは、以前から3次元化が進んできた。同じ構造の素子を積み上げるため、製造が比較的容易だったためだ。一方でCPUの分野では異なるチップを積むため、技術的に厳しいとされていた。

インテルは積み上げたチップを縦に貫通させる電極を工夫するなどして課題を克服。インテルのクリス・ウォーカー副社長は「パソコン業界を進化させるビジョンの試金石となる」と意気込む。来年以降、複数の機種に搭載される見通しだ。

背景には、半導体の性能を左右する「微細化」で後れを取っているとの危機感がある。チップに書き込む回路の線幅が小さくなるほどトランジスタの搭載量を増やせ、半導体の性能は向上する。

先頭を走るTSMCは今年、5ナノ(ナノは10億分の1)メートルの製品を米アップル向けに供給し始めた。韓国サムスン電子も供給準備を進める。

一方でインテルは1世代前の7ナノメートルのCPU開発に手間取り、量産は早くても22年になる見込みだ。7月の決算会見でボブ・スワン最高経営責任者(CEO)は「緊急対策の範囲内で(外部への)生産委託を検討する」と述べた。

回路の線幅が微細になるほど、半導体の量産に必要な設備投資も膨らむ。最先端の5ナノメートルの工場を新設するには、数兆円単位の資金が必要だ。インテルの19年の研究開発(R&D)と設備投資費用は296億ドル(約3兆円)に上った。

こうした苦境を打開するため、「インテルは微細化で後れを取った時点で、競合に先駆けて3次元積層の技術開発に取り組んだ」と、半導体業界関係者は指摘する。立体的にチップを積み重ねれば、同じ回路幅でも搭載するトランジスタ数を増やせるからだ。だが、追い上げは厳しい。

TSMCは協業

TSMCは顧客との協業を通じて3次元技術の開発を進める。足元ではグーグルと水面下で連携し、22年にも3次元製品の量産を始めるもようだ。

サムスン電子も8月、3次元パッケージ技術を使った7ナノメートルの半導体の試作に成功したと発表した。同社幹部は「3次元というイノベーションを駆使すれば半導体の限界を超えられる」と話す。

インテル共同創業者のゴードン・ムーア氏は1965年、CPU性能が1年半~2年で倍増するという「ムーアの法則」を提唱した。ただし、過去50年の進化をけん引した微細化技術は、物理的な限界に近づきつつある。

電子情報技術産業協会(JEITA)によると、IoTなどのデータ産業の世界の市場規模は30年に404兆円に達するという。今後も右肩上がりを続ける半導体業界でインテルが盟主の地位を保つには、3次元化を通じてムーアの法則を維持し続ける必要がある。